PUBLISHED BY

Microsoft Press

A Division of Microsoft Corporation

16011 NE 36th Way, Box 97017, Redmond, Washington 98073-9717

Copyright© 1987 by Richard Wilton

All rights reserved. No part of the contents of this book may

be reproduced or transmitted in any form or by any means without

the written permission of the publisher.

Library of Congress Cataloging in Publication Data

Wilton, Richard, 1953–

The programmer's guide to PC and PS/2 video systems.

Includes index.

1. IBM Personal Computer—Programming. 2. Expansion boards (Microcomputers).

3. Computer graphics. I. Title.

QA76.8.I2594W55 1987 005.265 87-20264

ISBN 1-55615-103-9

Printed and bound in the United States of America.

3 4 5 6 7 8 9 FGFG 8 9 0 9 8 7

Distributed to the book trade in the

United States by Harper & Row.

Distributed to the book trade in

Canada by General Publishing Company, Ltd.

Distributed to the book trade outside the

United States and Canada by Penguin Books Ltd.

Penguin Books Ltd., Harmondsworth, Middlesex, England

Penguin Books Australia Ltd., Ringwood, Victoria, Australia

Penguin Books N.Z. Ltd., 182-190 Wairau Road, Auckland 10, New Zealand

British Cataloging in Publication Data available

Acquisitions Editor: Claudette Moore

Technical Editor: Jeff Hinsch

IBM® is a registered trademark and PC/AT™, PC-DOS™, PC/XT™, and PS/2™ are trademarks of International Business Machines Corporation. Microsoft® and MS-DOS® are registered trademarks of Microsoft Corporation.

The material in Chapters 6, 7, and 8 owes a great deal to the original efforts of several respected workers in the field of computer graphics. In each of these chapters I have included references to some of their best-known publications. If you are intrigued by the algorithms described in these chapters, by all means obtain the original publications and explore them yourself.

This book could not have been written without the encouragement of my family, friends, and colleagues, who deserve great thanks for their patience and support. My gratitude also to Andy Fischer and to Charles Petzold, both of whom graciously reviewed portions of this book and offered accurate criticism and suggestions.

And, of course, my special thanks to the enthusiastic people at Microsoft Press—Claudette Moore, Jeff Hinsch, and many others—who painstakingly transformed the raw material of this book into the finished product.

I clearly remember the day I first plugged a new IBM Enhanced Graphics Adapter (EGA) into an IBM PC. It was good to have IBM's new “enhanced” video hardware, with its better resolution and control over colors, as well as features not found in any of IBM's earlier PC video hardware. Now I was ready to write some really sharp graphics applications.

Or so I thought. The problem was, I couldn't figure out how to program the contraption. I had no technical documentation at all. (It arrived in the mail six months and $125 later.) I tried disassembling the EGA's ROM BIOS, but studying 6000 uncommented machine instructions soon raised more questions than it answered. I desperately tried the shotgun approach—changing the contents of memory locations and machine registers just to see what would happen—but this was like chopping out random pieces of an automobile just to see what would stop working.

What I lacked was the details—conceptual descriptions of the hardware design, tables describing the programming interface, and, above all, source code examples for some typical programming techniques. A few well-chosen source code examples would have saved many hours of experimentation and frustration when I was trying to understand how to program that video adapter.

This book was inspired by the painful memory of that experience. It is filled with source code examples. Its text describes the source code, and vice versa. This book also has many tables and summary descriptions of the hardware programming interface. In short, this book is what I wish I'd had when I started to program PC video hardware.

The first chapter of this book is a general overview of the video display environment. It describes the commonly used PC and PS/2 video hardware the rest of the book deals with. It also introduces you (if you aren't already on speaking terms) to the well-known ROM BIOS video support routines.

The next 10 chapters contain the nuts and bolts of IBM video programming. The earlier chapters cover the fundamentals, including hardware architecture, video display modes, and the nature of the interface between your programs and the hardware. The later chapters build upon the fundamentals to demonstrate a number of techniques for producing text and graphics output.

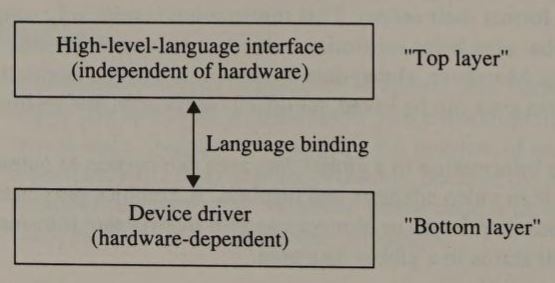

The last two chapters of this book take you to the low and high levels of video graphics programming. Chapter 12 is the hardware tinkerer's chapter—if you want to work with vertical interrupts or play with bit planes, this one's for you. Finally, Chapter 13 tells how to link your video hardware drivers to high-level programs and introduces you to several commercial video output packages.

This book is not really meant for beginners. That's not to say that a programmer who is just learning how to write working code will not benefit from this material. On the contrary, the many working examples of useful source code should be valuable to anyone who plans to do serious programming for PCs or PS/2s. Nevertheless, the broader your programming background, the more tools you will have for solving the diverse and exacting problems involved in video programming.

I use assembly language and C for most of the programming examples in this book, although I intentionally avoid some of C's more cryptic syntactic constructs. If you are comfortable with assembly language and with a high-level language such as C, Pascal, FORTRAN, PL/1, or structured BASIC, you should have no problem reading the source code examples.

Moreover, Chapter 13 discusses interfaces for several high-level languages using different memory models and subroutine-calling protocols. You can follow the guidelines there to convert any of the C-callable source code examples to the subroutine-calling protocol used by your favorite language translator.

You might want to use some other programming tools if you plan to experiment with the source code examples that follow. For example, a good assembly-language debugger can be extremely helpful. You will probably need an object linker if you plan to call the assembly- language routines in this book from high-level-language programs. Also, as source files and object modules proliferate, you might find a UNIX-like make utility quite useful in keeping things straight.

Everything in this book is intended to run under MS-DOS, or PC-DOS, version 2.0 or later. However, there is nothing in any of the source code that verifies which operating system is in use, so be careful if you transport the code to earlier versions of MS-DOS or to another operating system.

Having a PC or PS/2 with a video display attached is essential. Video programming is like swimming: It's one thing to read about it, but it's quite another experience to try it yourself. In fact, if you plan to do a great deal of video programming, you should consider installing two different video subsystems and displays in your PC. With two separate sets of video hardware in the same computer, you can run a debugger on one screen while a test program produces output on the other screen. This dual-display hardware configuration is a real timesaver, particularly when you're developing video graphics routines such as those described in Chapters 5 through 9.

Here is a list of the various computers and video adapters I used to develop the techniques discussed in this book:

IBM PC/XT IBM PC/AT IBM PS/2 Model 30 IBM PS/2 Model 60

IBM Monochrome Display Adapter IBM Color Graphics Adapter IBM Enhanced Graphics Adapter IBM PS/2 Display Adapter Hercules Graphics Card Hercules Graphics Card Plus Hercules Color Card Hercules InColor Card

If you are using one of these computers or adapters, or a hardware-compatible clone, then you should be able to run the source code examples.

To program IBM PC video hardware effectively, you need to know what the hardware is designed to do and how software and the system BIOS are expected to interact with it. This basic information is found in IBM's Technical Reference manuals for the PC, PC/XT, PC/AT, and PS/2s and in its Options and Adapters Technical Reference manuals. Most second-source manufacturers of IBM PC video equipment also provide detailed technical information on their hardware.

The material in this book is intended to complement the discussions in the manufacturers' technical documentation. I tried to follow the manufacturers' terminology and hardware descriptions wherever possible. However, the manufacturers' documentation goes somewhat awry at times. If you find a discrepancy between the official documentation and this book, you can (I hope) rely on this book to contain the right information.

Still, in a book this size, I have certainly made some mistakes. I welcome your comments, criticisms, and suggestions.

I have found that writing good video software is challenging, but the rewards are particularly satisfying. I hope to share some of the challenges—and some of the satisfaction—with you in this book.

Microcomputer video systems keep getting better. Since the introduction of the IBM PC in 1981, engineering technology has improved, and the market for more powerful video hardware has widened. Both IBM and its competitors have responded by developing increasingly sophisticated video adapters and displays, as well as the software to accompany them.

This chapter provides an overview of the evolution of IBM PC and PS/2 video hardware. This overview is by no means comprehensive, but it covers the most widely used video equipment that IBM and Hercules offer. The chapter concludes with an introduction to IBM's video BIOS, a set of drivers built into ROM in all IBM PCs and PS/2s, which provides a basic programming interface for video applications.

A “plain vanilla” IBM PC/XT or PC/AT contains no built-in video hardware, so you must select and install the video hardware yourself. In a typical configuration, a video display (monitor) is attached with a 9-wire cable to a video adapter installed inside the PC. A typical video adapter is a printed circuit board with a 9-pin connector that attaches to the monitor's cable and a 2-by-31-connection card-edge tab that inserts into one of the slots on the PC's motherboard. Figure 1-1 shows these connectors, as well as some of the integrated circuits common to many IBM video adapters. The circuitry in the video adapter generates the signals that control what is displayed on the monitor's screen.

When you purchase an IBM PC, you must decide which video adapter and monitor to use. The most widely used video adapters with the most software written for them are IBM's Monochrome Display Adapter, Color Graphics Adapter, and Enhanced Graphics Adapter, and the monochrome Graphics Card made by Hercules.

In contrast, all IBM PS/2 series computers are equipped with a built- in video subsystem, so purchasing a separate video adapter is unnecessary. The video subsystem in the PS/2 Models 25 and 30 is called the Multi-Color Graphics Array. In Models 50, 60, and 80, the integrated video subsystem is commonly known as the Video Graphics Array. The Video Graphics Array subsystem also is available as an adapter for the PC/XT, PC/AT, and PS/2 Model 30. This adapter has essentially the same hardware features as the integrated PS/2 subsystem.

When the PC was introduced in 1981, IBM offered two video adapters: the Monochrome Display Adapter (MDA) and the Color Graphics Adapter (CGA). The MDA is designed for use with a monochrome monitor (the IBM Monochrome Display) that displays 80 columns and 25 rows of alphanumeric text. The CGA supports either an RGB display (a monitor with separate input signals for red, green, and blue) or a home television set (which uses a composite video signal). The CGA, of course, can display graphics information on a dot-by-dot basis as well as alphanumeric text.

Even though both the MDA and the CGA can display 25 rows of 80-column text, most people find the MDA's green monochrome display easier on the eyes. This is because the monochrome display used with an MDA has significantly higher resolution than that of any monitor you can use with the CGA. Its resolution is 720 dots wide and 350 dots high; the maximum resolution of a CGA-driven display is 640 dots wide and 200 dots high.

Both adapters display characters in a rectangular matrix of dots. A simple calculation shows that each character is 9 dots wide and 14 dots high on a Monochrome Display but only 8-by-8 dots on a CGA display. The MDA's higher resolution produces more crisply defined characters that are easier to read. For this reason, most PC users who need to read text prefer an MDA to a CGA.

On the other hand, many computer users need to display charts, diagrams, and other graphics information in addition to alphanumeric text. Also, displaying colors on the screen is essential to many computer applications. Because the MDA can display only monochrome text, PC users who need graphics output can compromise by using the CGA, with its dot-by-dot color graphics capability but less-readable text.

Why not just attach the higher-resolution monochrome display to a Color Graphics Adapter and get the best of both worlds? Unfortunately, the video signals generated by an MDA are incompatible with those required to drive a CGA monitor, and vice versa. Mismatching the monitor and the adapter leads to a malfunctioning monitor instead of a higher-resolution display.

If you need sharp, readable text as well as color graphics, and you can afford the extra equipment, you can install both an MDA and a CGA in the same PC. You can then use the monochrome display (attached to the MDA) for text processing and an RGB color display (driven by the CGA) for color graphics.

Hercules' solution to the problem of displaying readable text and dot-by-dot graphics on the same monitor was to add graphics capability to a monochrome display adapter. The monochrome Hercules Graphics Card (HGC), introduced in 1982, can display graphics and alphanumeric text on the same green monochrome display that is used with an IBM MDA. (In addition to its graphics capabilities, the HGC exactly duplicates the function of IBM's original MDA.) The ability to display a combination of readable text and monochrome graphics is sufficient for many applications, so many PC users find the HGC an economical option. Because it has received support from major software vendors, the HGC has become firmly established in the marketplace.

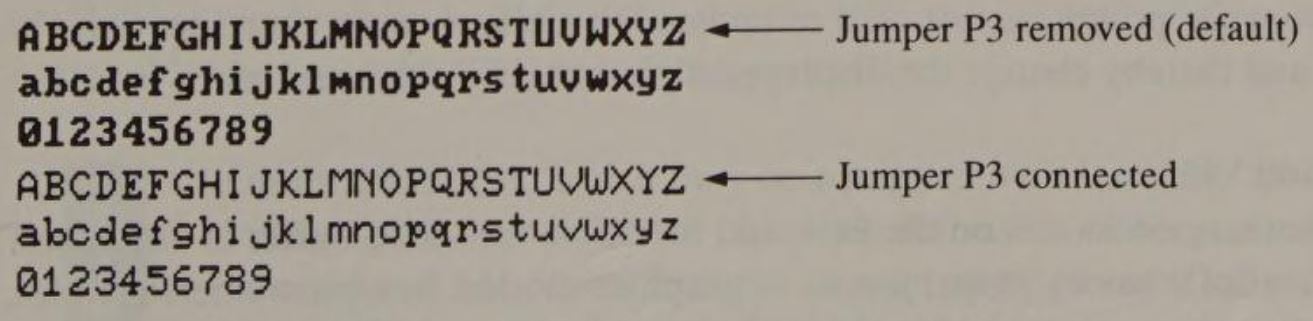

The HGC+ was released in June 1986. The big difference in this upgrade of the original HGC is that it can display customized, RAM-based alphanumeric character sets, whereas the MDA and HGC can display only one, predefined, ROM-based alphanumeric character set. Because alphanumeric characters can be displayed much more rapidly than dot- by-dot graphics characters, using the HGC+ can double or triple the speed of some text-oriented applications.

A different response to the demand for better text and graphics resolution is IBM's Enhanced Graphics Adapter (EGA), released in early 1985. The EGA can be configured to emulate either an MDA or a CGA; what makes the EGA “enhanced” is that it can also do things its predecessors cannot. Unlike the MDA, the EGA can produce dot-by-dot graphics on a monochrome display. Furthermore, the EGA improves on the CGA with the ability to generate 16-color alphanumeric or graphics images with 640-by-350 resolution.

Although the resolution and color capabilities of the EGA are not that much greater than those of the CGA, both text and graphics appear much sharper on the EGA than on the CGA. The availability of low-priced EGA clones and of high-quality software applications that exploit the adapter's capabilities have made the EGA a de facto hardware standard in the marketplace.

The Hercules InColor Card, introduced in April 1987, is essentially a 16-color version of the HGC+. The InColor hardware fully emulates the HGC+, so programs that run properly on the HGC+ can run without change on the InColor Card. The InColor Card's resolution is the same as that of the HGC and HGC+: 720 horizontal by 348 vertical pixels. The adapter's color capabilities equal those of the EGA. It can display 16 colors at once from a palette of 64 colors. The adapter must be used with an EGA-compatible color display that has 350-line vertical resolution.

Don't confuse the InColor Card with the Hercules Color Card, an augmented CGA clone designed for use in the same computer with an HGC or HGC+.

The Multi-Color Graphics Array (MCGA) is the video subsystem integrated into the PS/2 Models 25 and 30. From a programmer's perspective, the MCGA resembles the CGA in many ways, yet the MCGA has much better resolution (a maximum of 640 horizontal by 480 vertical dots) and improved color-display capabilities.

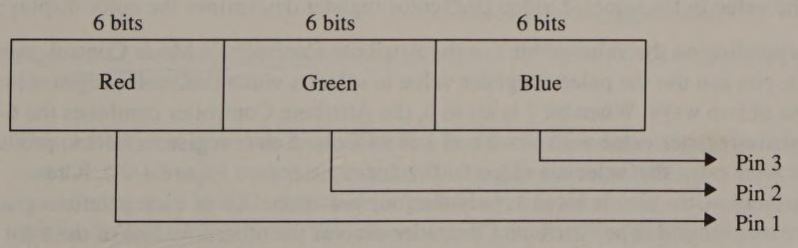

A significant difference between the MCGA and the above video adapters is that the MCGA generates analog RGB video signals, whereas the others produce digital RGB signals. The difference between digital and analog RGB is something like the difference between an on-off wall switch and a dimmer switch. With digital RGB signals, the video display must recognize only whether the signal for a particular color (red, green, or blue) is on or off. On the other hand, a video display that uses analog RGB signals translates the voltage of each signal into a wide range of corresponding color intensities. Only an analog video display can be used with the MCGA.

Some video monitors can be configured for either analog or digital video signals. If you use the right cable, these monitors can be connected to an MCGA if they are configured for analog video.

The justification for using analog video is that it can display a wider range of colors. The MCGA has a video Digital to Analog Converter (DAC) that enables the subsystem to display as many as 256 different colors at once from a palette of 262,144 (256 K or 2^18) colors. In addition to an analog color display, IBM supplies an analog monochrome display for use with the MCGA. With a monochrome monitor, the MCGA can display as many as 64 shades of gray.

The term Video Graphics Array (VGA) refers specifically to part of the circuitry of the video subsystem in PS/2 Models 50, 60, and 80. The VGA is actually a single chip that integrates the same set of functions performed by several chips on the EGA. Nevertheless, people generally use the abbreviation VGA to describe the entire video subsystem.

The VGA's programming interface is similar to the EGA's, so many programs written for the EGA will run unchanged on the VGA. The VGA is capable of somewhat higher display resolution (as much as 720-by-400 in text modes, or 640-by-480 in graphics modes). Like the MCGA, however, the VGA contains a video DAC that can generate 256 colors at a time from a possible 262,144. Because the VGA generates the same analog RGB signals as the MCGA, it must be used with the same analog monochrome or color monitors.

A set of BIOS (Basic Input/Output System) routines in ROM is built into every IBM PC and PS/2. The ROM BIOS routines provide an interface to standard hardware features, including the time-of-day clock, the keyboard, floppy and hard disks, and of course the video subsystem. The video BIOS routines comprise a set of simple tools for performing basic video programming tasks such as writing strings of characters to the screen, erasing the screen, changing colors, and so on.

Although the ROM BIOS video routines are sometimes slow and relatively unsophisticated, programs that use them are portable among different video subsystems in IBM PCs and PS/2s. Furthermore, most manufacturers of IBM PC clones have duplicated the functions of IBM's BIOS in their machines. Thus, a program that uses BIOS routines to access the video hardware is likely to be more portable than one that does not.

The BIOS routines are written in assembly language, so accessing them is easiest when you program in assembly language. All BIOS video routines are accessed by executing 80x86 software interrupt 10H. (The term 80x86 refers to the microprocessors in the Intel 8086 family: 8086, 8088, 80286, and 80386.) For this reason, the ROM BIOS video interface is widely known as the INT 10H interface. The ROM BIOS supports a number of video input/output functions, each accessed by executing interrupt 10H. The functions are numbered; before executing interrupt 10H, you place the number of the desired function in 80x86 register AH.

At the time the interrupt is executed, the remaining 80x86 registers usually contain parameters to be passed to the BIOS routines. If the INT 10H function returns data to your program, it does so by leaving the data in one or more of the 80x86 registers. This register-based parameter-passing protocol is intended for use in assembly-language programs.

To see how the INT 10H interface is typically used, examine the assembly-language routine SetVmode() in Listing 1-1. This routine can be linked with a program written in Microsoft C. (The underscore preceding the procedure name, the near keyword in the PROC declaration, and the use of the stack to pass parameters all follow Microsoft C conventions.) The heart of the routine is its call to the ROM BIOS to configure the video hardware for a particular video mode. (The details of this operation are discussed in Chapter 2 and in Appendix A.)

TITLE 'Listing 1-1'

NAME SetVmode

PAGE 55,132

;

; Name: SetVmode

;

; Function: Call IBM PC ROM BIOS to set a video display mode.

;

; Caller: Microsoft C:

;

; void SetVmode(n);

;

; int n; /* video mode */

;

ARGn EQU byte ptr [bp+4] ; stack frame addressing

EQUIP_FLAG EQU byte ptr ds:[10h] ; (in Video Display Data Area)

CGAbits EQU 00100000b ; bits for EQUIP_FLAG

MDAbits EQU 00110000b

_TEXT SEGMENT byte public 'CODE'

ASSUME cs:_TEXT

PUBLIC _SetVmode

_SetVmode PROC near

push bp ; preserve caller registers

mov bp,sp

push ds

mov ax,40h

mov ds,ax ; DS -> Video Display Data Area

mov bl,CGAbits ; BL := bits indicating presence of CGA

mov al,ARGn ; AL := desired video mode number

mov ah,al ; test if desired mode is monochrome

and ah,7

cmp ah,7

jne L01 ; jump if desired mode not 7 or 0Fh

mov bl,MDAbits ; BL := bits indicating presence of MDA

L01: and EQUIP_FLAG,11001111b

or EQUIP_FLAG,bl ; set bits in EQUIP_FLAG

xor ah,ah ; AH := 0 (INT 10h function number)

push bp

int 10h ; call ROM BIOS to set the video mode

pop bp

pop ds ; restore caller registers and return

mov sp,bp

pop bp

ret

_SetVmode ENDP

_TEXT ENDS

ENDThe actual call to the video BIOS is simple. First, the desired function number is placed into register AH (XOR AH,AH). Then, after preserving the contents of register BP on the stack (PUSH BP), the routine invokes the ROM BIOS function by executing interrupt 10H (INT 10H).

In Listing 1-2, a complementary routine called GetVmode() interrogates the BIOS for the number of the current video mode. The routine obtains this number by executing interrupt 10H function 0FH. The ROM BIOS function leaves the mode number in register AL. GetVmode() then returns the number to the calling program.

TITLE 'Listing 1-2'

NAME GetVmode

PAGE 55,132

;

; Name: GetVmode

;

; Function: Call IBM PC ROM BIOS to set a video display mode.

;

; Caller: Microsoft C:

;

; int GetVmode();

;

_TEXT SEGMENT byte public 'CODE'

ASSUME cs:_TEXT

PUBLIC _GetVmode

_GetVmode PROC near

push bp ; preserve caller registers

mov bp,sp

mov ah,0Fh ; AH := 0Fh (INT 10h function number)

push bp

int 10h ; call ROM BIOS to get video mode number

pop bp

xor ah,ah ; AX := video mode number

mov sp,bp

pop bp

ret

_GetVmode ENDP

_TEXT ENDS

ENDThe code that precedes the actual call to the ROM BIOS in Listing 1-1 modifies one of several global variables that reflect the status of the PC's video subsystem. These variables are updated and referenced by all ROM BIOS video routines. They are collected in a block of RAM called, in IBM's technical documentation, the Video Display Data Area (or Video Control Data Area). The Video Display Data Area consists of two blocks of RAM. The first block is found between memory locations 0040:0049 and 0040:0066, the second between 0040:0084 and 0040:008A.

Some video BIOS routines also reference a 2-bit field in a global variable at 0040:0010 (called EQUIP_FLAG in IBM's technical documentation). Bits 4 and 5 of this variable indicate a default video mode to be used when the computer is first booted. The code in SetVmode() updates this bit field to conform with the video mode being selected. For example, if a Monochrome Display Adapter (MDA) is required for the desired video mode, the bit field in EQUIP_FLAG is updated accordingly. (Again, details on ROM BIOS video modes are found in Chapter 2 and in Appendix A.)

Throughout this book are references to the INT 10H interface, the BIOS's Video Display Data Area, and the symbolic names of specific locations in the Video Display Data Area that are of particular interest. If you aren't already familiar with the available INT 10H functions and the contents of the Video Display Data Area, a perusal of Appendix A might be very helpful.

You can make ROM BIOS routines accessible in high-level language programs with an assembly-language routine such as SetVmode() or GetVmode(). Listings 1-3 and 1-4 are short C programs that can be executed as MS-DOS commands. The program in Listing 1-3 calls SetVmode() to select a video mode. This program may be executed interactively or from a batch file. The program in Listing 1-4 calls GetVmode() and returns the video mode number in a way that can be used in a batch file (that is, with IF ERRORLEVEL == commands).

/* Listing 1-3 */

main( argc, argv )

int argc;

char **argv;

{

int ModeNumber;

void SetVmode();

if (argc != 2) /* verify command line syntax */

{

printf( "\nSyntax: SETVMODE n\n" );

exit( 1 );

}

sscanf( argv[1], "%x", &ModeNumber ); /* get desired mode number */

SetVmode( ModeNumber ); /* call ROM BIOS via INT 10h */

}/* Listing 1-4 */

main()

{

int GetVmode();

return( GetVmode() );

}The overall process of generating an executable file for one of these programs consists of compiling the C code to produce an object module, assembling the assembly-language code to produce another object module, and linking the object modules to create the executable file. If the C source code in Listing 1-3 is contained in a file named SM.C and the assembly code in Listing 1-1 is saved in SETVMODE.ASM, you can build the executable file SM.EXE as follows:

msc sm; (compile the C code)

masm setvmode; (assemble the subroutine)

link sm+setvmode; (link the object modules)

Some high-level language compilers can generate appropriate object code for loading the 80x86 registers, executing interrupt 10H, and copying the results from the registers to the calling program. If your compiler has this capability, you might prefer to access the INT 10H interface directly, instead of linking an assembly- language subroutine to your high-level program. For example, Listing 1-5 uses Microsoft C's int86() function to implement GetVmode().

/* Listing 1-5 */

#include "dos.h"

main()

{

struct BYTEREGS regs; /* BYTEREGS defined in dos.h */

regs.ah = 0x0F; /* AH=0x0F (ROM BIOS function number) */

int86( 0x10, ®s, ®s ); /* perform interrupt 10h */

return( (int)regs.al );

}Many other INT 10H functions are available in the ROM BIOS. Your application program accesses them by loading the appropriate registers and executing interrupt 10H. Although the INT 10H support for video input/output admittedly is less than perfect, it is widely used in operating-system software (including MS-DOS) as well as in countless applications. If you want to write effective video and graphics programs, become familiar with the capabilities and the limitations of the INT 10H interface.

This chapter describes IBM PC and PS/2 video hardware from a programmer's point of view. It covers the basics: which parts of the computer's video subsystem can be programmed, how a program interacts with the hardware, and how calculations for changing the video display format are performed. Many of the programming techniques in later chapters are based on the fundamental information discussed here.

The purpose of this chapter is to demystify the hardware programming interface. Because most programmers rely on the video BIOS to perform most, if not all, hardware-level programming in their applications, an aura of mystery surrounds the way software interacts with video hardware. Of course, after you learn about it, you may wish it had remained a mystery--but the more you know, the more your programs will be able to do with the video hardware.

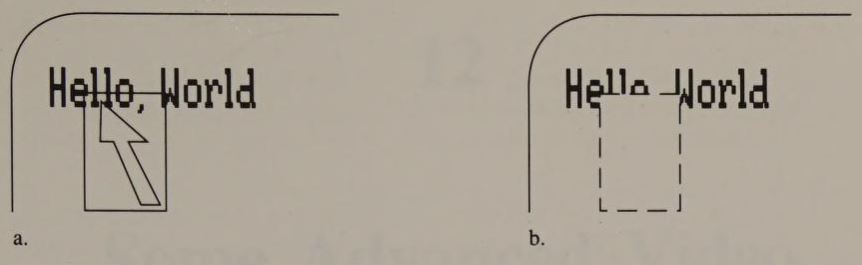

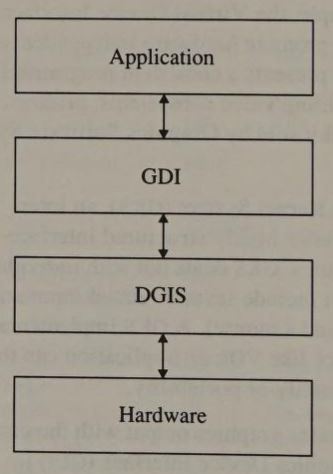

As you write programs that interact with IBM video hardware, it helps to visualize the relationships among the programmable components of IBM video subsystems (see Figure 2-1). You do not need a circuit designer's understanding of the hardware to write a good video interface. You do need to know where and how your program can interact with the hardware to produce video output efficiently.

The most tangible part of a computer's video hardware is the monitor, or video display. However, there's nothing you can directly program in the monitor's hardware. It is the computer's video subsystem that contains programmable hardware. The signals generated by the video subsystem control what appears on the screen.

The monitor differs from a home television receiver in that a group of separate timing and color signals drives it. In contrast, a home TV decodes a single “composite” signal that contains timing, color, and audio information. Although some IBM PC video adapters can generate such composite video output signals, as well as the direct drive signals that computer monitors use, most people avoid using a home television with their computers. Both text and colors appear sharper on a computer monitor than they do on a composite television screen.

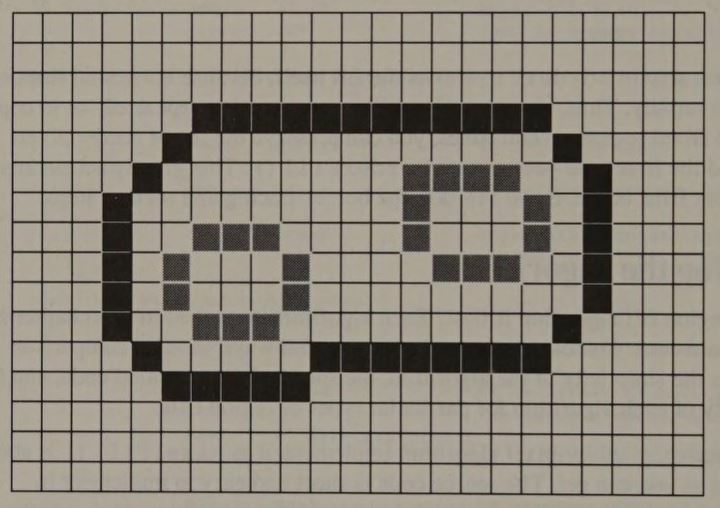

All the video monitors discussed in this book are raster-scan devices. The image on the screen of a monitor is made up of a group of closely spaced horizontal lines called the raster. An electron beam scans each successive line from left to right, starting at the upper left corner of the display. As the beam sweeps each line, the color and brightness of each of several hundred points (pixels) in the line are varied, and the entire raster appears as a coherent image.

Conceptually, you can regard the electron beam as having “color” and “intensity,” but in color video monitors the beam actually comprises three separate electron beams. Each beam controls the display of one of the three primary video colors (red, green, and blue) on the screen. Each pixel on a color display is physically represented by a small, closely spaced triad of red, green, and blue luminescent dots or stripes of phosphor. The three electron beams are masked in such a way that each illuminates dots of only one primary color. Thus, the relative intensity of the beams as they sweep over each triad determines the color and brightness of the pixels. Of course, unless you use a magnifying glass or look closely at the display, you do not perceive the red, green, and blue dots individually, but rather as blended colors.

The video buffer is a block of RAM in the video subsystem where displayable data is stored. This RAM lies within the address space of the computer's CPU, so a program may read from and write to the video buffer in the same way it accesses any other portion of RAM.

The video subsystem's display circuitry updates, or refreshes, the screen by continually and repeatedly reading the data in the video buffer. Each bit or group of bits in the video buffer specifies the color and brightness of a particular location on the screen. The screen is refreshed between 50 and 70 times a second, depending on which video subsystem is in use. Obviously, when a program changes the displayed contents of the video buffer, the screen changes almost immediately.

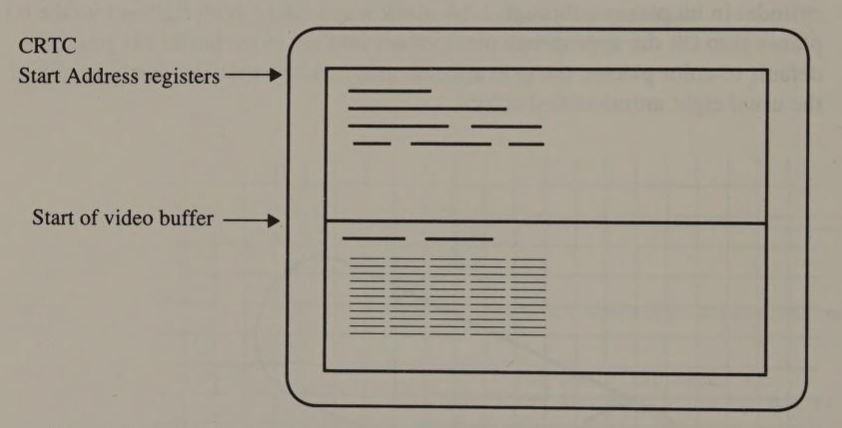

The actual amount of RAM available as a video buffer varies with the video subsystem. Most IBM video subsystems incorporate video buffers large enough to hold more than one screen of displayable data, so only part of the buffer is visible on the screen at any time. (Chapter 3 discusses how to make full use of available video RAM.)

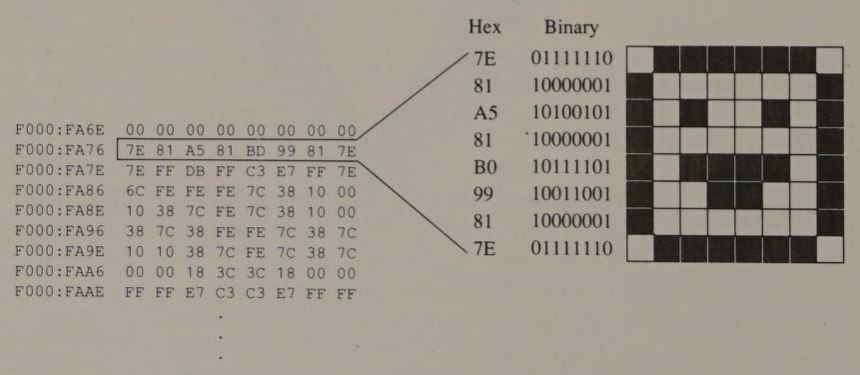

All IBM video subsystems incorporate hardware that reads and decodes the data in the video buffer. For example, an alphanumeric character generator translates ASCII codes from the video buffer into the dot patterns that make up characters on the screen. An attribute decoder translates other data in the video buffer into the signals that produce colors, underlining, and so forth. Software can control these and other specialized components of the video subsystem; later chapters describe such programming in detail.

The CRT Controller (or CRTC for short) generates horizontal and vertical timing signals. It also increments a video buffer address counter at a rate that is synchronized with the timing signals. The video display circuitry reads data from the video buffer using the CRTC's address value, decodes the data, and sends the resulting color and brightness signals to the monitor along with the CRTC's timing signals. In this way the CRTC synchronizes the display of data from the video buffer with the timing signals that drive the video display.

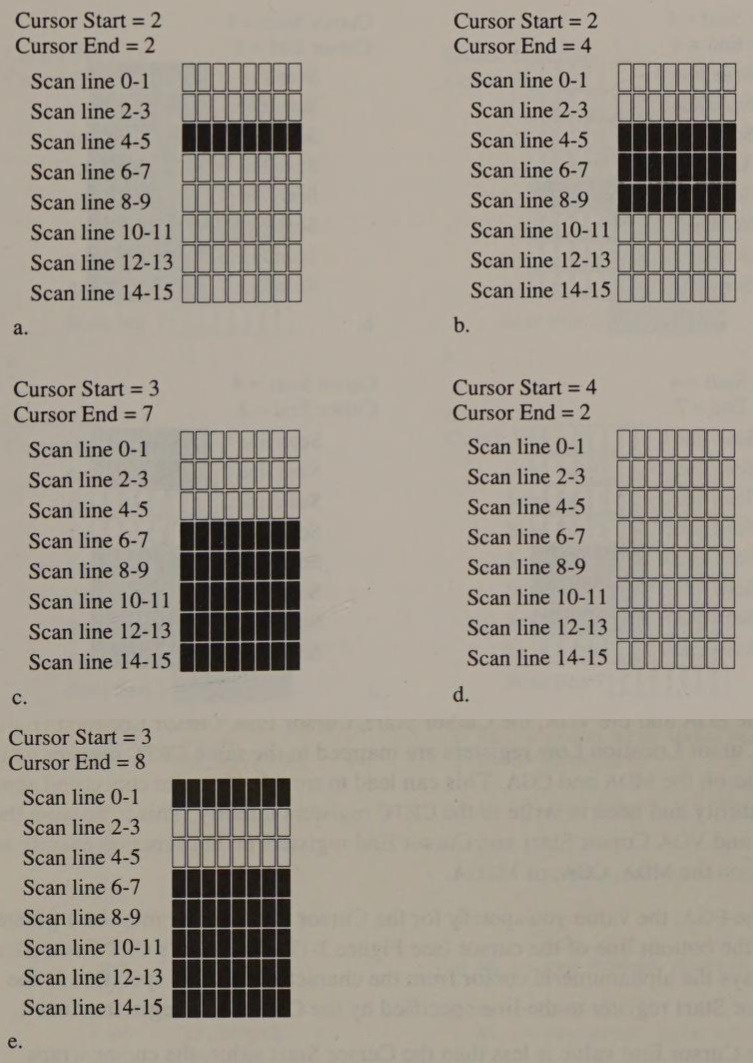

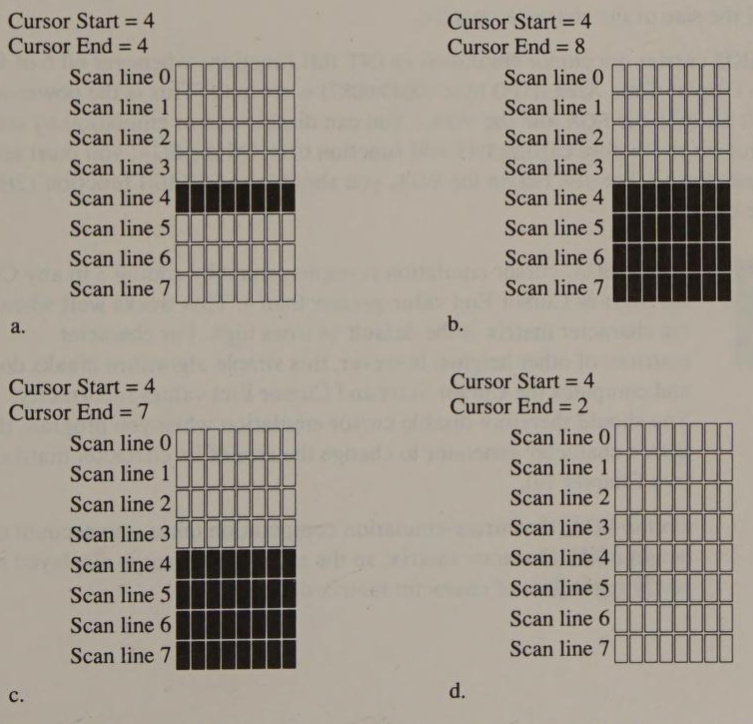

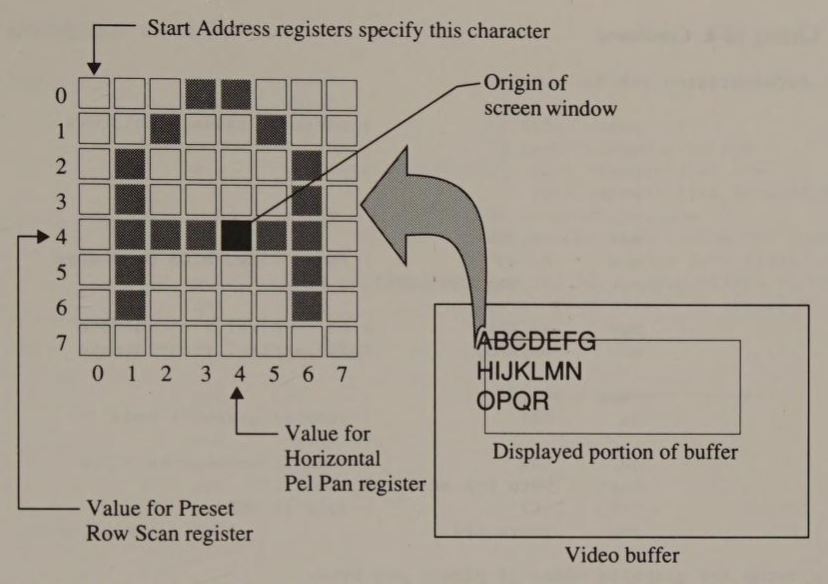

The CRTC performs several other miscellaneous functions. Among them are determining the size and displayed position of the hardware cursor, selecting the portion of the video buffer to be displayed, locating the hardware underline, and detecting light pen signals. (Chapter 3 contains examples of CRTC programming for some of these functions.)

On the MDA, CGA, and Hercules cards, the CRTC is a single chip, the Motorola 6845. On the EGA, the CRTC is a custom LSI (large-scale integration) chip designed by IBM. On the MCGA, the CRTC is part of its Memory Controller Gate Array. The VGA's CRTC is one component of the single-chip Video Graphics Array. Regardless of the hardware implementation, the CRTC can be programmed to generate a variety of timing parameters in all these subsystems. Before delving into the techniques of CRTC programming, however, it is worthwhile to review how the CRTC's timing signals control the monitor's display of a raster-scan video image.

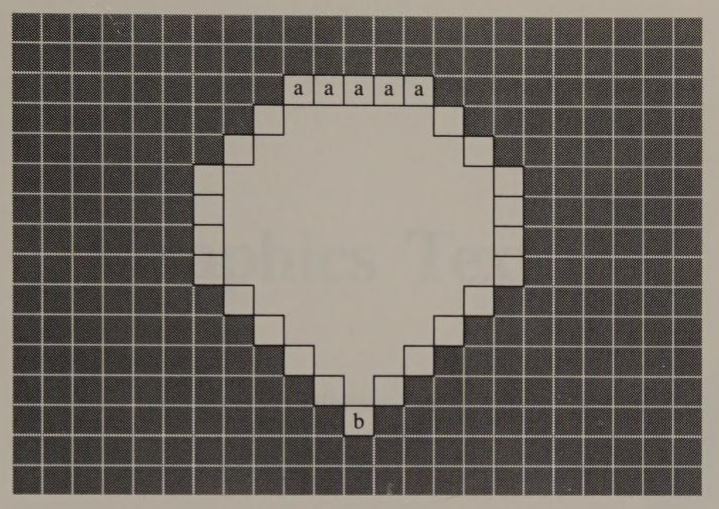

The video image is refreshed in a cyclic manner between 50 and 70 times a second, depending on the configuration of the video subsystem. During each refresh cycle, the electron beam sweeps across the screen in a zigzag fashion, starting at the left side of the topmost horizontal line in the raster (see Figure 2-2). After scanning a line from left to right, the beam is deflected down to the start of the next line until the entire raster is scanned. Then the beam returns to the upper left corner of the display, and the cycle repeats.

A number of carefully timed events occur as the beam moves across the display. At the beginning of each line, the electron beam is turned on in response to a Display Enable signal that the CRTC generates. As the beam sweeps left to right across the line, the video display circuitry uses the CRTC's address counter to read a sequence of bytes from the video buffer. The data is decoded and used to control the color and brightness signals sent to the monitor. As the beam sweeps across the screen, its color and brightness vary in response to these signals.

Near the screen's right edge, the CRTC turns off the Display Enable signal and no further data is displayed from the video buffer. The CRTC then generates a horizontal sync signal, which causes the monitor to deflect the electron beam leftward and downward to the start of the next horizontal line in the raster. Then the CRTC turns the Display Enable signal back on to display the next line of data.

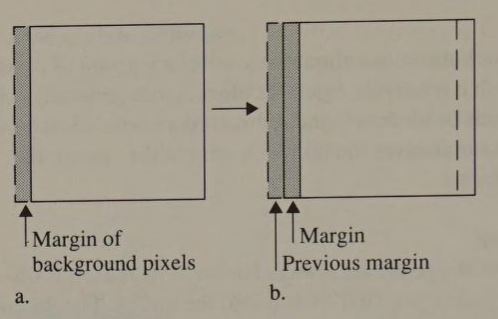

The short period of time between the end of one line of video data and the beginning of the next is called the horizontal blanking interval. Because the horizontal retrace interval (the amount of time required to deflect the beam to the start of the next line) is shorter than the horizontal blanking interval, a certain amount of horizontal overscan is generated on both ends of each line (see Figure 2-3).

During periods of horizontal overscan, the electron beam can be left on, displaying an overscan, or border, color. However, the primary reason horizontal overscan is designed into a video subsystem is to provide a margin of error in centering the raster, so that no data is lost at the edges of the screen.

Once the electron beam has scanned all horizontal lines in the raster, the Display Enable signal is turned off. The CRTC then generates a vertical sync signal, which tells the monitor to deflect the electron beam from the bottom of the screen back to the upper left corner. The vertical retrace interval (during which the beam travels from the bottom to the top of the screen) is shorter than the vertical blanking interval (during which no data from the video buffer is displayed), so there are areas of vertical overscan at the top and bottom of the raster (see Figure 2-3). Like horizontal overscan, vertical overscan provides a border as well as a safety margin so that the raster can be centered on the screen.

The CRTC programming interface is well defined and easy to use. The same general programming approach applies to all IBM PC and PS/2 video subsystems.

The Monochrome Display Adapter's CRTC, the Motorola 6845, has nineteen 8-bit internal data registers. The contents of each register control various characteristics of the timing signals generated by the 6845 (see Figure 2-4). One of these registers is an address register; its contents indicate which of the other 18 can be accessed. Most of the registers are write-only, but registers 0EH and 0FH, which control the position of the hardware cursor, may be read as well as written. On the MDA, the 6845's Address register is mapped to an I/O port at 3B4H, and the remaining 18 registers are all mapped to the next I/O port at 3B5H.

To access the 6845's data registers, you first write the register number to the 6845's Address register (I/O port 3B4H). Then you access the specified data register with an I/O write or read at port 3B5H. For example, Listing 2-1 shows how to determine the current cursor location by reading the contents of registers 0EH and 0FH on the 6845. These two registers (Cursor Location High and Cursor Location Low) contain the high-order and low-order bytes of the cursor location relative to the start of the video buffer.

| Register | Name | Read/Write Access |

|---|---|---|

| 00H | Horizontal Total | Write only |

| 01H | Horizontal Displayed | Write only |

| 02H | Horizontal Sync Position | Write only |

| 03H | Horizontal Sync Pulse Width | Write only |

| 04H | Vertical Total | Write only |

| 05H | Vertical Total Adjust | Write only |

| 06H | Vertical Displayed | Write only |

| 07H | Vertical Sync Position | Write only |

| 08H | Interlace Mode | Write only |

| 09H | Maximum Scan Line | Write only |

| 0AH | Cursor Start | Write only |

| 0BH | Cursor End | Write only |

| 0CH | Start Address High | Write only |

| 0DH | Start Address Low | Write only |

| 0EH | Cursor Location High | Read/Write |

| 0FH | Cursor Location Low | Read/Write |

| 10H | Light Pen High | Read only |

| 11H | Light Pen Low | Read only |

mov ax,40h

mov es,ax ; ES := video BIOS data segment

mov dx,es:[63h] ; DX := 3x4h (3B4h or 3D4h)

mov al,0Eh

out dx,al ; select 6845 Cursor Location

; High register

inc dx

in al,dx ; read selected register at 3x5h

mov ah,al ; AH := high byte of cursor

; location

dec dx

mov al,0Fh

out dx,al ; select Cursor Location Low register

inc dx

in al,dx ; AX := offset of cursor relative

; to start of video buffer

; convert to character row and column

mov dx,es:[4Eh] ; DX := CRT_START (buffer start offset

; in bytes

shr dx,1 ; convert to words

sub ax,dx ; subtract from cursor offset

div byte ptr es:[4Ah] ; divide by CRT_COLS

xchg ah,al ; AH := row, AL := columnWith the MDA, there is rarely any reason to change the values in any of the 6845 registers except 0AH and 0BH (Cursor Start and Cursor End) and 0EH and 0FH (Cursor Location High and Low). Registers 00H through 09H control the horizontal and vertical timing signals, which should not be changed. Registers 0CH and 0DH (Start Address High and Start Address Low), which indicate what part of the MDA's video buffer is displayed, should always be set to 0.

The Color Graphics Adapter's CRTC is a Motorola 6845, as is the MDA's. The same programming technique used to access the CRTC on the MDA also works on the CGA. On the CGA, however, the CRTC Address register is mapped to I/O port 3D4H and the data registers are accessed at 3D5H. If you write a program that can run on either an MDA or a CGA, you can take advantage of the fact that the video BIOS routines in both the PC and PS/2 families maintain the value of the CRTC's Address register I/O port in a variable. Many of the programming examples in this book reference this variable, ADDR_6845, which is located at 0040:0063 in the BIOS Video Display Data Area.

Like the MDA and CGA, the Hercules Graphics Card, Graphics Card Plus, and InColor Card all use a Motorola 6845 as a CRTC. The CRTC registers are mapped at I/O ports 3B4H and 3B5H on all Hercules adapters. Although it is a color adapter, the InColor Card uses the MDA's I/O port and video buffer addresses in order to preserve compatibility with the MDA and with Hercules monochrome adapters.

On all Hercules video adapters (as well as the EGA, MCGA, and VGA), you can set both the address and data registers of the CRTC with one 16-bit port write (OUT DX,AX) instead of two 8-bit port writes (OUT DX,AL). For example, the two sequences of code that follow do the same thing to the CRTC.

mov dx,3B4h ; CRTC address register

mov al,0Ch ; CRTC register number

out dx,al ; select this register

inc dx ; DX := 3B5h (CRTC data register)

mov al,8 ; data

out dx,al ; store data in register

dec dxand

mov dx,3B4h ; CRTC address register

mov ax,080Ch ; AL := reg number, AH := data

out dx,ax ; store data in registerThe Enhanced Graphics Adapter's CRTC is a proprietary LSI chip with a set of registers different from those in the 6845 (see Figure 2-5). The programming interface is similar to the 6845's, but the register assignments and formats are different enough that programs that write directly to CRTC registers on the MDA or CGA will probably crash on an EGA.

The EGA's CRTC supports a wider set of control functions than does the 6845. For example, the CRTC can cause a hardware interrupt at the start of a vertical blanking interval. The CRTC also supports the simultaneous display of two noncontiguous portions of the video buffer. (Chapter 12 describes these CRTC capabilities.)

A curious feature of the EGA's CRTC is its Overflow register (07H). Because the EGA can display a raster of more than 256 lines, the CRTC registers that contain a number of scan lines must be 9 bits wide instead of 8. The high-order bit in each of these registers is stored in the Overflow register.

| Register | Name | Read/Write Access |

|---|---|---|

| 00H | Horizontal Total | Write only |

| 01H | Horizontal Display Enable End | Write only |

| 02H | Start Horizontal Blanking | Write only |

| 03H | End Horizontal Blanking | Write only |

| 04H | Start Horizontal Retrace | Write only |

| 05H | End Horizontal Retrace | Write only |

| 06H | Vertical Total | Write only |

| 07H | Overflow | Write only |

| 08H | Preset Row Scan | Write only |

| 09H | Maximum Scan Line Address | Write only |

| 0AH | Cursor Start | Write only |

| 0BH | Cursor End | Write only |

| 0CH | Start Address High | Read/Write |

| 0DH | Start Address Low | Read/Write |

| 0EH | Cursor Location High | Read/Write |

| 0FH | Cursor Location Low | Read/Write |

| 10H | Vertical Retrace Start | Write only |

| 10H | Light Pen High | Read only |

| 11H | Vertical Retrace End | Write only |

| 11H | Light Pen Low | Read only |

| 12H | Vertical Display Enable End | Write only |

| 13H | Offset (Logical Line Width) | Write only |

| 14H | Underline Location | Write only |

| 15H | Start Vertical Blanking | Write only |

| 16H | End Vertical Blanking | Write only |

| 17H | Mode Control | Write only |

| 18H | Line Compare | Write only |

In the MCGA, the functions of a CRTC are integrated into a circuit component called the Memory Controller Gate Array. The first 16 Memory Controller registers are analogous to those in the 6845 (see Figure 2- 6). As on the CGA, all MCGA Memory Controller registers, including the CRTC registers, are indexed through an address register at I/O port 3D4H. The data registers themselves may be accessed at port 3D5H.

Several features of the MCGA's CRTC distinguish it from the CGA's 6845. All of the Memory Controller registers can be read as well as written. Moreover, registers 00H through 07H may be designated read- only so that horizontal and vertical timing parameters are not inadvertently disrupted. Setting bit 7 of the Memory Controller Mode Control register (10H) to 1 protects registers 00H through 07H.

Another feature of the MCGA CRTC is that the hardware can compute the horizontal timing parameters for each of the available video modes. When bit 3 of the Mode Control register is set to 1, and when the values in registers 00H through 03H represent appropriate horizontal timing values for 40-by-25 alphanumeric mode (video BIOS mode 0), the Memory Controller generates proper horizontal timing signals in all available video modes.

If you compare the MCGA CRTC and the Motorola 6845 register by register, you will note several discrepancies in the interpretation of the values stored in some CRTC registers. In particular, the values expected in registers 09H, 0AH, and 0BH are specified in units of two scan lines on the MCGA, instead of one scan line on the 6845. Because the default alphanumeric character matrix on the MCGA is 16 scan lines high, this feature provides a certain amount of low-level compatibility, letting you use the same values for these registers as you would on a CGA.

| Register | Name | Read/Write Access |

|---|---|---|

| 00H | Horizontal Total | Read/Write |

| 01H | Horizontal Displayed | Read/Write |

| 02H | Start Horizontal Sync | Read/Write |

| 03H | Sync Pulse Width | Read/Write |

| 04H | Vertical Total | Read/Write |

| 05H | Vertical Total Adjust | Read/Write |

| 06H | Vertical Displayed | Read/Write |

| 07H | Start Vertical Sync | Read/Write |

| 08H | (reserved) | |

| 09H | Scan Lines per Character | Read/Write |

| 0AH | Cursor Start | Read/Write |

| 0BH | Cursor End | Read/Write |

| 0CH | Start Address High | Read/Write |

| 0DH | Start Address Low | Read/Write |

| 0EH | Cursor Location High | Read/Write |

| 0FH | Cursor Location Low | Read/Write |

| 10H | Mode Control | Read/Write |

| 11H | Interrupt Control | Read/Write |

| 12H | Character Generator, Sync Polarity | Read/Write |

| 13H | Character Generator Pointer | Read/Write |

| 14H | Character Generator Count | Read/Write |

| 20-3FH | (reserved) |

Functionally, the VGA's CRTC registers (see Figure 2-5) comprise a superset of those in the EGA's CRTC. The VGA's CRTC register set is addressable at the same I/O ports as the EGA's. A few more bit fields have been added to the register set, primarily so that the CRTC can handle 400-line and 480-line rasters. However, unlike the EGA's CRTC, the VGA's CRTC does not support the use of a light pen.

More important, however, all the EGA's CRTC register specifications have been carried over to the VGA. Thus, programs that write to the EGA's CRTC registers can be run unchanged on VGA-based hardware.

As on the MCGA, the VGA's CRTC data registers can all be read as well as written. Also, the VGA horizontal and vertical timing registers (CRTC registers 00H through 07H) can be write-protected by setting bit 7 of the Vertical Retrace End register (11H) to 1.

As on Hercules adapters, you can program the CRTC on the EGA, MCGA, and VGA using a 16-bit port write (OUT DX,AX). Moreover, you will find by experimenting that 16-bit port writes work on many non-IBM video adapters. But stay away from this technique on MDAs, CGAs, and clones if portability is important.

To use the CRTC effectively, you must be able to perform the basic computations necessary to specify the CRTC's timings correctly. These computations are based on three constraints: the bandwidth of the video signal sent to the monitor and the monitor's horizontal and vertical synchronization rates.

IBM PC video subsystems display pixels at a rate determined by the hardware. This rate is variously known as the video bandwidth, the dot rate, or the pixel rate; the oscillator that generates this rate is called the dot clock. The MDA, CGA, and Hercules adapter use only one dot clock; on the EGA and VGA, more than one dot clock is available (see Figure 2‑7). The higher the dot clock frequency, the better the displayed pixel resolution.

Given the dot rate, the CRTC must be programmed so that the horizontal and vertical scan frequencies sent to the video display are limited to frequencies the display can handle. Older displays, such as the IBM Monochrome Display, are designed to handle only one horizontal and one vertical scan rate. Newer displays, such as the NEC MultiSync, can synchronize with a range of horizontal and/or vertical scan rates.

| IBM Subsystem | Video Bandwidth (Dot Rate) in MHz | Horizontal Scan Rate in KHz | Vertical Scan Rate in Hz |

|---|---|---|---|

| MDA, HGC | |||

| 720x350 mono | 16.257 | 18.43 | 50 |

| CGA | |||

| 640x200 color | 14.318 | 15.75 | 60 |

| EGA | |||

| 640x350 color | 16.257 | 21.85 | 60 |

| 640x200 color | 14.318 | 15.75 | 60 |

| 720x350 mono | 16.257 | 18.43 | 50 |

| InColor | |||

| 720x350 color | 19.000 | 21.80 | 60 |

| MCGA | |||

| 640x400 mono/color | 25.175 | 31.50 | 70 |

| 640x480 mono/color | 25.175 | 31.50 | 60 |

| VGA | |||

| 640x400 mono/color | 25.175 | 31.50 | 70 |

| 720x400 mono/color | 28.322 | 31.50 | 70 |

| 640x480 mono/color | 25.175 | 31.50 | 60 |

| 640x350 mono/color | 25.175 | 31.50 | 70 |

Consider how you would calculate the typical CRTC register values shown in Figure 2-8 for an MDA with an IBM Monochrome Display. The MDA's video bandwidth (dot rate) is 16.257 MHz; that is, 16,257,000 dots per second. The monochrome display's horizontal scan rate is 18.432 KHz (18,432 lines per second). Dividing the dot rate by the horizontal scan rate gives 882 dots per line. Each character displayed by the MDA is 9 dots wide, so the total number of characters in each line is 882 / 9, or 98.

This value is used to program the CRTC's Horizontal Total register. For the MDA's CRTC, a Motorola 6845, the value you store in the Horizontal Total register must be 1 less than the computed total, or 97 (61H).

| Register | Name | Parameter | Description |

|---|---|---|---|

| 00H | Horizontal Total | 97 (61H) | (total characters per scan line) - 1 |

| 01H | Horizontal Displayed | 80 (50H) | Characters displayed in each scan line |

| 02H | Horizontal Sync Position | 82 (52H) | Position in scan line where horizontal retrace starts |

| 03H | Horizontal Sync Width | 15 (0FH) | Duration of horizontal retrace interval (character clocks) |

| 04H | Vertical Total | 25 (19H) | Total character rows in one frame |

| 05H | Vertical Total Adjust | 2 | Remaining scan lines in one frame |

| 06H | Vertical Displayed | 25 (19H) | Character rows dis- played in each frame |

| 07H | Vertical Sync Position | 25 (19H) | Position in frame where vertical retrace starts |

| 08H | Interlace Mode | 2 | Always set to 2 |

| 09H | Maximum Scan Line | 13 (0DH) | (height of one charac- ter in scan lines) - 1 |

In terms of CRTC timings, the Horizontal Total value describes the amount of time, in “character clocks,” required to complete one horizontal scan. During this period, 80 characters are actually displayed. (This is the value used for the Horizontal Displayed register.) The other 18 character clocks are spent in horizontal overscan and in horizontal retrace.

The duration of the horizontal retrace interval is about 10 to 15 percent of the Horizontal Total value. The exact value depends on the video subsystem. On the MDA, the horizontal retrace interval is set at 15 character clocks by storing this value in the CRTC Horizontal Sync Width register. This leaves 3 character clocks of horizontal overscan. The horizontal retrace signal is programmed to start 2 character clocks after the rightmost displayed character by storing the value 82 (52H) in the CRTC Horizontal Sync Position register. Thus, there are 2 character clocks of right horizontal overscan and 1 character clock of left overscan.

Changing the value in the Horizontal Sync Position register changes the size of the right and left overscan areas and thus the horizontal position of the displayed raster. For example, to shift the displayed raster to the left, increase the size of the right overscan interval by increasing the value in the CRTC Horizontal Sync Position register.

Similar considerations apply in programming the CRTC to generate appropriate vertical timings. The nominal horizontal scan rate in the MDA's monochrome display is 18.432 KHz (18,432 lines per second) with a vertical scan rate of 50 Hz (50 frames per second), so the number of lines in one frame is 18,432 / 50, or 368. Since each character displayed is 14 lines high, 25 rows of characters account for 350 lines. The MDA's CRTC always uses 16 lines for vertical retrace; this leaves 368 - (350 + 16), or 2 lines of vertical overscan.

The CRTC programming follows these calculations. The height of each displayed character is specified by the value in the CRTC Maximum Scan Line register. Since characters are 14 scan lines high, the maximum scan line value is 13 (0DH). Taken together, the values for Vertical Total (25 character rows) and Vertical Total Adjust (2 scan lines) indicate the total number of scan lines in one frame. The number of character rows displayed (25) is indicated in the Vertical Displayed register. The position in the frame where vertical retrace starts (25) is specified by the value in the Vertical Sync Position register.

The CRTCs on the MCGA, EGA, and VGA are more complex than the Motorola 6845 CRTC on the MDA and CGA. Nevertheless, the registers that control horizontal and vertical timings in the newer video subsystems are similar in nomenclature and functionality to the 6845's registers. The computations for the MCGA, EGA, and VGA CRTCs are derived from the dot rate, the character size, and the horizontal and vertical capabilities of the video display, just as they are for the MDA and CGA.

All IBM video subsystems have a read-only CRT Status register. This register is located at I/O port 3BAH on the MDA and Hercules adapters and at 3DAH on the CGA and MCGA; on the EGA and VGA, this register is at 3BAH in monochrome configurations and at 3DAH in color configurations. Generally, two of the eight bits in this register reflect the current status of the horizontal and vertical timing signals generated by the CRTC. These status bits can be used to synchronize video buffer updates with the screen refresh cycle to minimize interference with the displayed image. (Chapter 3 contains examples of this type of programming.)

Unfortunately, the exact interpretation of the status bits in the CRT Status register varies among the different IBM video subsystems (see Figure 2-9). Therefore, programs should be designed to determine which hardware they are running on (Appendix C) before they attempt to use the status information in this register.

Listing 2-2 shows how the status bits in the CRTC Status register are used to synchronize program operation with the video refresh cycle. This subroutine can be used on the CGA to time the horizontal blanking interval. The subroutine uses bit 3 of the CRT Status register, which indicates when the CRTC's vertical sync signal is active, to synchronize with the start of a refresh cycle. The loops at L01 and L02 show how this is done.

The loops at L03 and L04 then synchronize with the Display Enable signal, using bit 0 of the CRT Status value. When the Display Enable signal goes off, the loop at L05 decrements the value in CX during the horizontal blanking interval, that is, while the Display Enable signal is off. The number of iterations counted in CX can then be used as a timeout value to determine when the last horizontal line in the frame has been scanned. (See Chapter 3.)

TITLE 'Listing 2-2'

NAME HRTimeout

PAGE 55,132

;

; Name: HRTimeout

;

; Function: Determine a timeout value for the horizontal blanking interval

;

; Caller: Microsoft C:

;

; int HRTimeout();

;

_TEXT SEGMENT byte public 'CODE'

ASSUME cs:_TEXT

PUBLIC _HRTimeout

_HRTimeout PROC near

push bp ; usual C prologue to establish

mov bp,sp ; stack frame

mov ax,40h

mov es,ax ; ES := video BIOS data segment

mov dx,es:[63h] ; DX := port for CRTC Address register

add dl,6 ; DX := port for CRTC Status register

; synchronize with start of refresh cycle

L01: in al,dx ; AL := CRTC status

test al,8 ; test bit 3

jz L01 ; loop while NOT in vertical retrace

L02: in al,dx

test al,8

jnz L02 ; loop during vertical retrace

; synchronize with a horizontal scan and time the horizontal blanking interval

mov cx,0FFFFh ; CX := loop counter

cli ; disable interrupts

L03: in al,dx

test al,1

jnz L03 ; loop while Display Enable is inactive

L04: in al,dx

test al,1

jz L04 ; loop while Display Enable is active

L05: in al,dx

test al,1

loopnz L05 ; decrement CX and loop while Display

; Enable is inactive

sti ; enable interrupts again

mov ax,cx ; AX := loop counter

neg ax

shl ax,1 ; AX := timeout value

mov sp,bp ; discard stack frame and return to C

pop bp

ret

_HRTimeout ENDP

_TEXT ENDS

ENDDespite the timing constraints imposed by the dot clock and the rated horizontal and vertical scan rates of available monitors, all IBM video subsystems except the MDA can be programmed with a variety of different CRTC parameters. This makes a number of video modes available. Each video mode is characterized by its resolution (the number of characters or pixels displayed horizontally and vertically), by the number of different colors that can be displayed simultaneously, and by the format of the displayable data in the video buffer.

The horizontal and vertical resolution in a video mode is a function of the dot rate as well as the monitor's horizontal and vertical scan rates. The number of pixels displayed in each frame corresponds to the dot rate divided by the vertical scan rate. The actual horizontal and vertical resolution then depends on the horizontal scan rate.

| Register | Bit 7 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|

| MDA | 3BA | Video drive | 1 = horizontal sync | |||

| HGC, HGC+, InColor | 3BA | 0 = vertical sync | Video drive | 1 = light pen | 1 = horizontal sync | |

| trigger | ||||||

| CGA | 3DA | 1 = vertical sync | 1 = light pen switch closed | 1 = light pen trigger | 0 = display enable | |

| EGA | 3BA or 3DA | 1 = vertical sync | 1 = light pen switch closed | 1 = light pen trigger | 0 = display enable | |

| VGA | 3BA or 3DA | 1 = vertical sync | 0 = display enable | |||

| MCGA | 3DA | 1 = vertical sync* | 0 = display enable |

*0 = vertical sync in 640-by-480 2-color mode

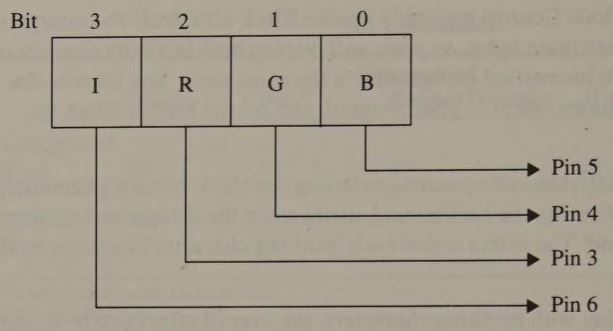

The number and variety of colors that can be displayed in a video mode depend on the design of the video subsystem's attribute decoding and video signal generator components. The attribute decoder uses data stored in the video buffer to control the color and brightness signals produced by the video signal generator. Establishing a particular video mode always involves programming a video subsystem's attribute decoder in addition to updating its CRTC parameters.

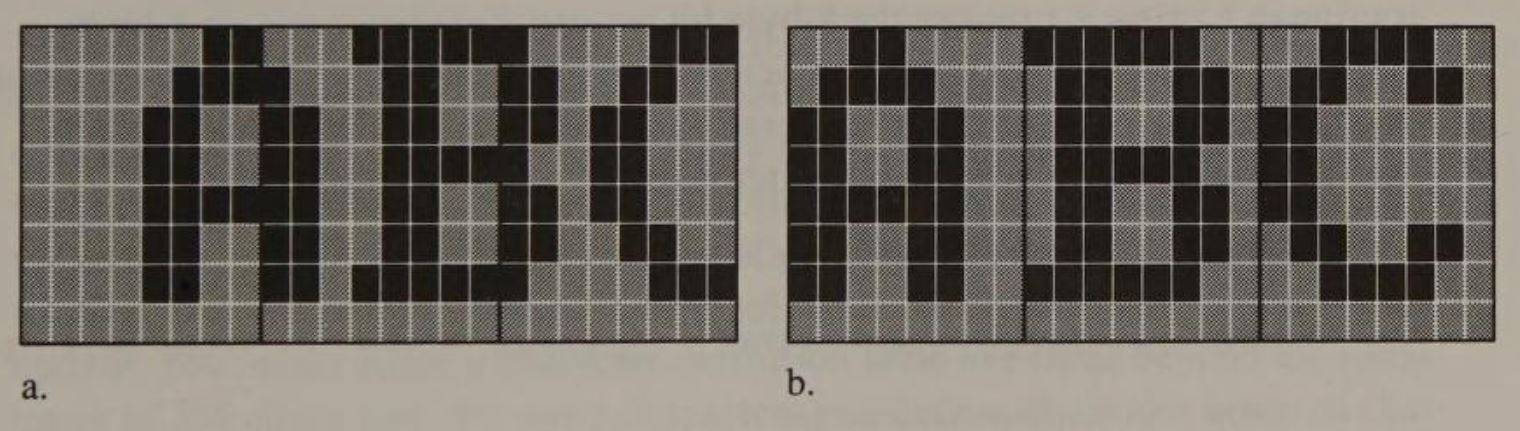

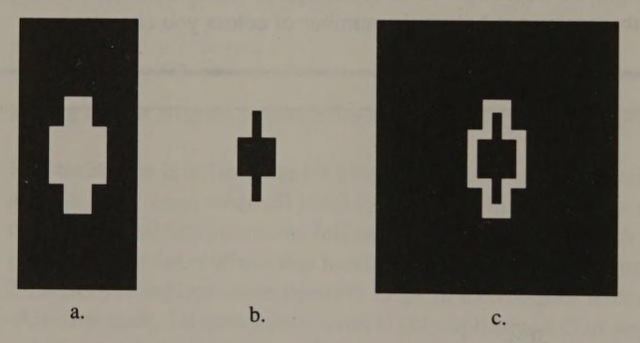

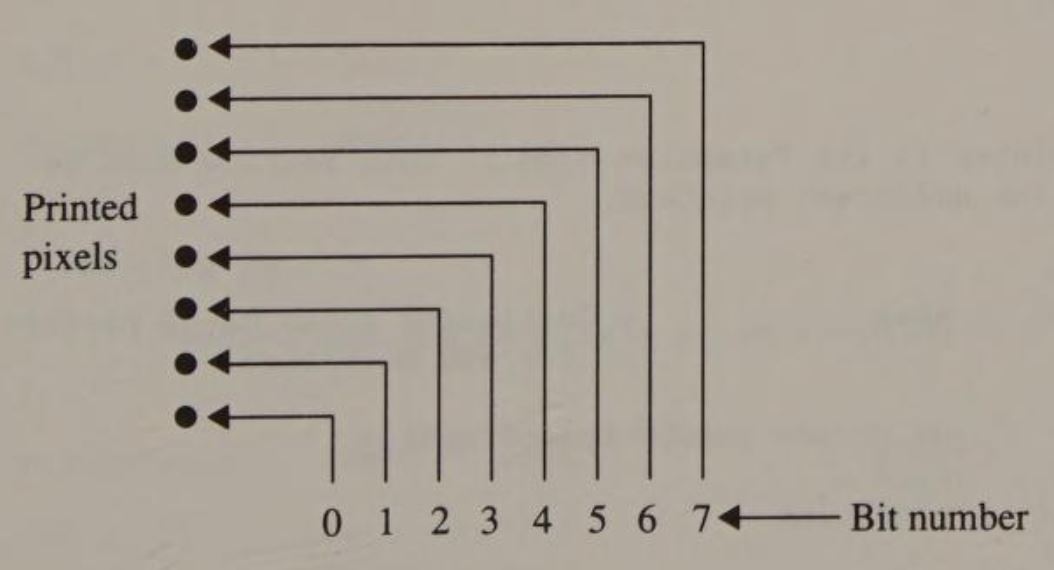

The format of the data in video RAM also characterizes a video mode. In all PC and PS/2 subsystems, video modes can be classified as alphanumeric or graphics modes, depending on the video buffer data format. In alphanumeric modes, the data in the video buffer is formatted as a sequence of ASCII code and attribute byte pairs; the alphanumeric character generator translates the ASCII codes into displayed characters while the attribute bytes specify the colors used to display them (see Chapter 3). In graphics modes, the video buffer is organized as a sequence of bit fields; the bits in each field designate the color of a particular pixel on the screen.

Establishing a video mode on an IBM PC or PS/2 video subsystem generally requires specific mode control programming apart from specifying CRTC parameters. For example, the alphanumeric character generator must be enabled in alphanumeric modes and disabled in graphics modes. Also, the subsystem's internal character clock, which determines the number of pixels generated for each alphanumeric character code read from the video buffer, may run at different rates in different video modes. These and other internal functions are controlled by loading one or more specialized mode control registers with values appropriate for each video mode.

The MDA's Mode Control register is a write-only register mapped to port 3B8H (see Figure 2-10). Only three of the eight bits in this register have meaning. Bit 0 is set to 1 at powerup and must always remain set to 1. Bit 3, when set to 1, enables video refresh; clearing this bit blanks the screen. Bit 5 is the Enable Blink bit; it controls whether characters can blink. On the MDA, most programs leave bit 3 set at all times. Chapter 3 explains how to use bit 5 (the Enable Blink bit).

| Bit | Settings |

|---|---|

| 0 | 1 = adapter enabled (should always = 1) |

| 1 | (unused, should always = 0) |

| 2 | (unused, should always = 0) |

| 3 | 1 = video enabled 0 = video disabled (screen blank) |

| 4 | (unused, should always = 0) |

| 5 | 1 = blinking attribute enabled 0 = blinking attribute disabled |

| 6 | (unused, should always = 0) |

| 7 | (unused, should always = 0) |

The Mode Control register on the CGA and MCGA is found at 3D8H (see Figure 2-11a). The five low-order bits control internal timings appropriate for the video modes they select, while bit 5 is an Enable Blink bit just as it is on the MDA. The useful bit patterns for the CGA's Mode Control register are listed in Figure 2-11b. These values correspond to the available BIOS video modes on the CGA.

The Mode Control registers on the CGA and the MCGA have two differences. One is that the MCGA Mode Control register may be read as well as written; the CGA register is write-only. The other difference relates to the function of bit 2. On the CGA, setting bit 2 to 1 disables the color burst component of the composite video output signal. This can improve the quality of the display if you are using a composite green or amber monitor with a CGA. On the MCGA, which does not support a composite monitor, the function of bit 2 of the Mode Control register is to select between two sources for the foreground color in 2-color graphics modes.

| Bit | Settings |

|---|---|

| 0 | 1 = 80-character alphanumeric modes 0 = 40-character alphanumeric modes |

| 1 | 1 = 320-wide graphics mode 0 = (all other modes) |

| 2 | 1 = color burst disabled (CGA only) 1 = foreground color from video DAC register 7 (MCGA only) 0 = color burst enabled (CGA only) 0 = foreground color from the video DAC register specified in bits 0-3 of the Palette register (3D9H) (MCGA only) |

| 3 | 1 = video enabled 0 = video disabled (screen blank) |

| 4 | 1 = 640-wide graphics modes 0 = (all other modes) |

| 5 | 1 = blinking attribute enabled 0 = blinking attribute disabled |

| 6 | (unused, should always = 0) |

| 7 | (unused, should always = 0) |

| BIOS Mode Number | Description | Value for Mode Control Register |

|---|---|---|

| 0 | 40x25 alpha (color burst disabled) | 00101100b (2CH) |

| 1 | 40x25 alpha | 00101000b (28H) |

| 2 | 80x25 alpha (color burst disabled) | 00101101b (2DH) |

| 3 | 80x25 alpha | 00101001b (29H) |

| 4 | 320x200 graphics | 00101010b (2AH) |

| 5 | 320x200 graphics (color burst disabled) | 00101110b (2EH) |

| 6 | 640x200 graphics | 00011100b (1CH) |

| 7 | 80x25 alpha (MDA only) | 00101001b (29H) |

| 11H | 640x480 graphics (MCGA only) | 00011000b (18H) |

The MCGA has two additional mode control registers, which are not implemented on the CGA. The MCGA Memory Controller Mode Control register (10H) at port 3D4H/3D5H selects 640-by-480 2-color and 320- by-200 256-color graphics modes (see Figure 2-12). An Extended Mode Control register is mapped to I/O port 3DDH. This register is used only during machine coldstart; it has no practical use in applications programs.

| Bit | Settings |

|---|---|

| 0 | 1 = select 320x200 256-color mode 0 = (all other modes) |

| 1 | 1 = select 640x480 2-color mode 0 = (all other modes) |

| 2 | (reserved) |

| 3 | 1 = horizontal timing parameters computed for video mode 0 = horizontal timing parameters as specified in registers 00-03H |

| 4 | 1 = enable dot clock (should always be 1) |

| 5 | (reserved) |

| 6 | Inverse of bit 8 of Vertical Displayed register (06H) |

| 7 | 1 = write-protect registers 00-07H 0 = allow updating of registers 00-07H |

The Hercules Graphics Card has two control registers whose contents affect the video mode configuration. The Mode Control register at 3B8H is functionally compatible with the MDA's Mode Control register, but it maps additional mode configuration functions to bits 1 and 7 (see Figure 2-13). Bit 1, when set to 1, establishes internal timings for a 720-by-348 graphics mode. Setting bit 7 to 1 while the adapter is in graphics mode displays the second half of the adapter's 64 KB video buffer at B800:0000. These bits have no function, however, unless the appropriate bits in the adapter's Configuration Switch register are set properly.

The Configuration Switch register (3BFH) determines the function of the Mode Control register at 3B8H (see Figure 2-14). When bit 0 of the Configuration Switch register is 0, the HGC cannot be placed in its graphics mode, so bit 1 of the Mode Control register must also be 0. Bit 1 of the Configuration Switch register controls video buffer addressing when the adapter is used in combination with a CGA or compatible (see below).

| Bit | Settings |

|---|---|

| 0 | (unused) |

| 1 | 1 = 720x348 graphics mode 0 = 80x25 alphanumeric mode |

| 2 | (unused, should always = 0) |

| 3 | 1 = video enabled 0 = video disabled (screen blank) |

| 4 | (unused, should always = 0) |

| 5 | 1 = blinking attribute enabled 0 = blinking attribute disabled |

| 6 | (unused, should always = 0) |

| 7 | 1 = graphics mode buffer displayed from B800:0000 (video page 1) 0 = graphics mode buffer displayed from B000:0000 (video page 0) |

The HGC+ and InColor Card implement an extended mode control register (called the xMode register) in addition to the Mode Control and Configuration Switch registers found on the HGC. The xMode register is a write-only register addressable as register 14H at port 3B4H/3B5H. (The register is addressed exactly as if it were a CRTC register.) The xMode register controls the alphanumeric character generator; Chapter 10 explains this in detail.

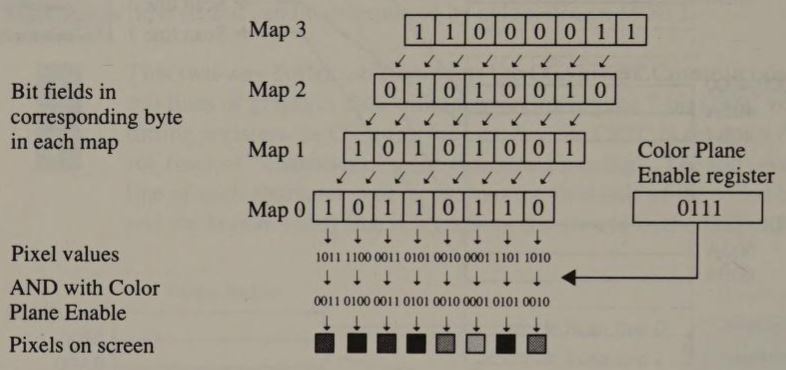

When you establish a video mode on the EGA and the VGA, you can control the internal timing and addressing of several different components of the video subsystem. These include the Sequencer, the Graphics Controller, and the Attribute Controller, each of which has several control registers. There is also a Miscellaneous Output register, which controls I/O port and video buffer addressing and selects the dot clock frequency.

All Sequencer, Graphics Controller, and Attribute Controller registers on the EGA are write-only registers, but on the VGA they can be read as well as written.

The Sequencer generates internal timings for video RAM addressing. It has five programmable data registers (see Figure 2-15) mapped to ports 3C4H and 3C5H in a manner analogous to CRTC register mapping. The Sequencer's Address register is located at 3C4H; its five data registers are selected by storing an index value between 0 and 4 in the Address register and then accessing the corresponding data register at 3C5H.

| Register | Name |

|---|---|

| 0 | Reset |

| 1 | Clocking Mode |

| 2 | Map Mask |

| 3 | Character Map Select |

| 4 | Memory Mode |

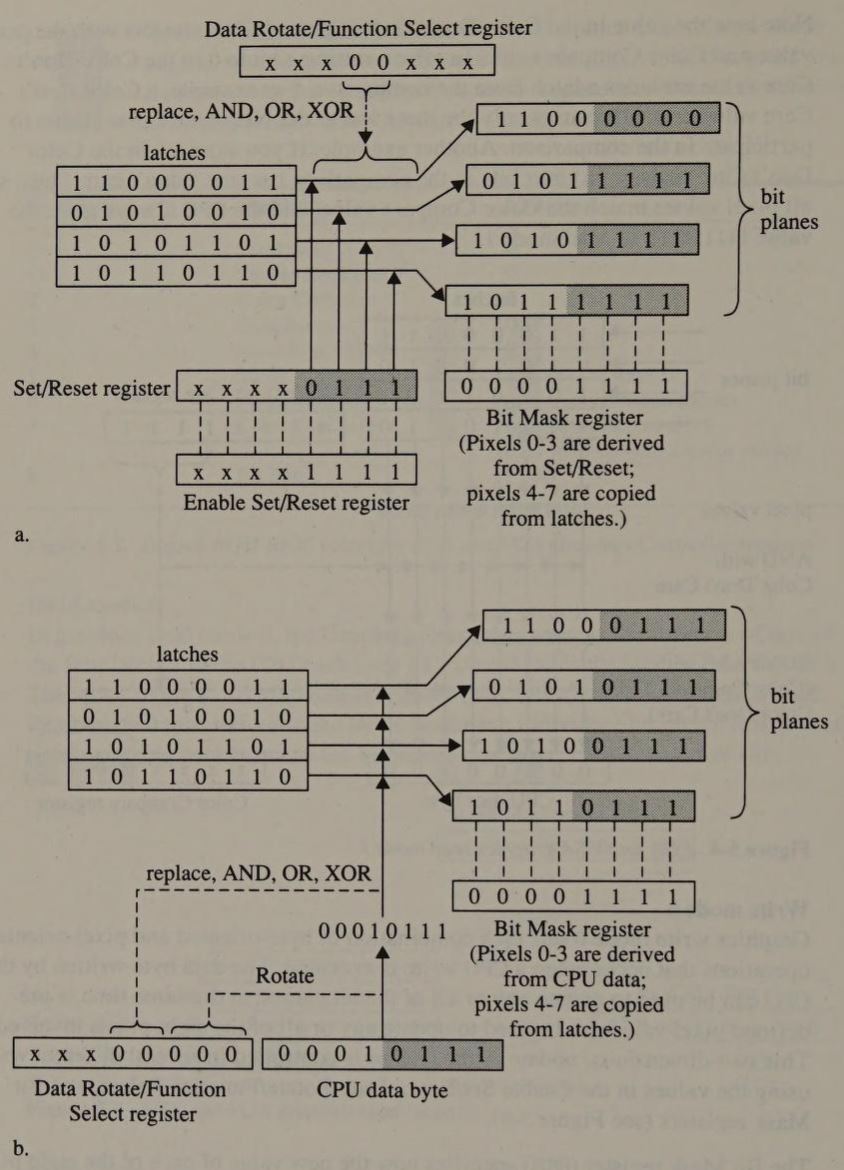

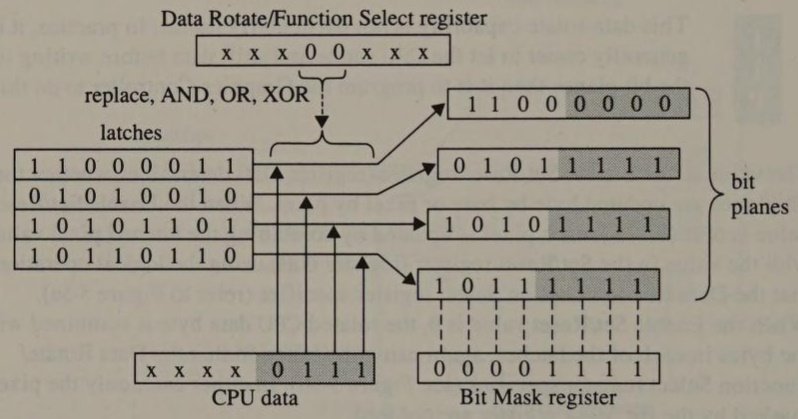

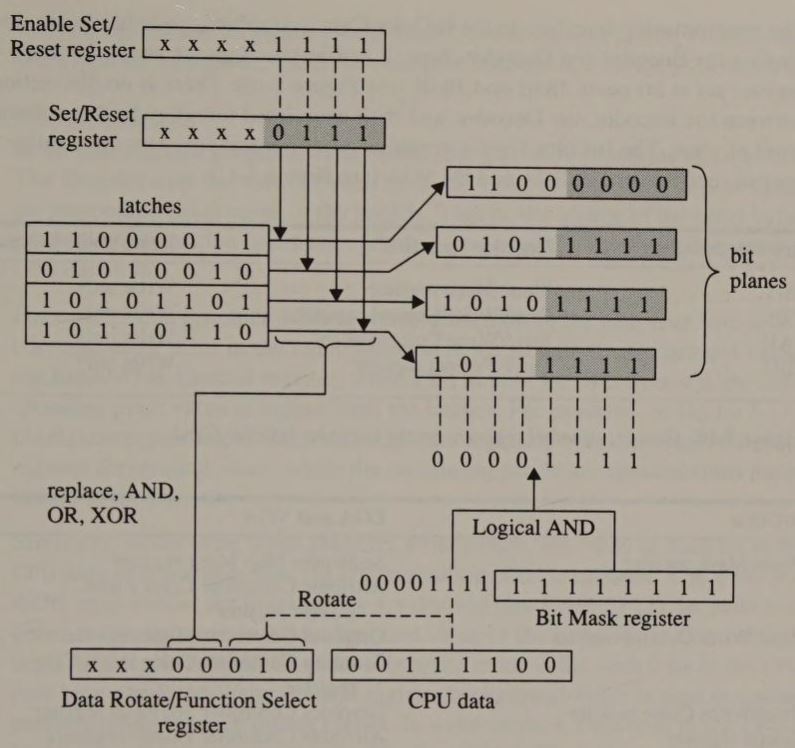

The Graphics Controller mediates data flow between the video buffer and the CPU, as well as from the video buffer to the Attribute Controller. The Graphics Controller has nine data registers, plus an Address register (see Figure 2-16). The Address register maps to port 3CEH, and the data registers map to port 3CFH.

| Register | Name |

|---|---|

| 0 | Set/Reset |

| 1 | Enable Set/Reset |

| 2 | Color Compare |

| 3 | Data Rotate/Function Select |

| 4 | Read Map Select |

| 5 | Graphics Mode |

| 6 | Miscellaneous |

| 7 | Color Don't Care |

| 8 | Bit Mask |

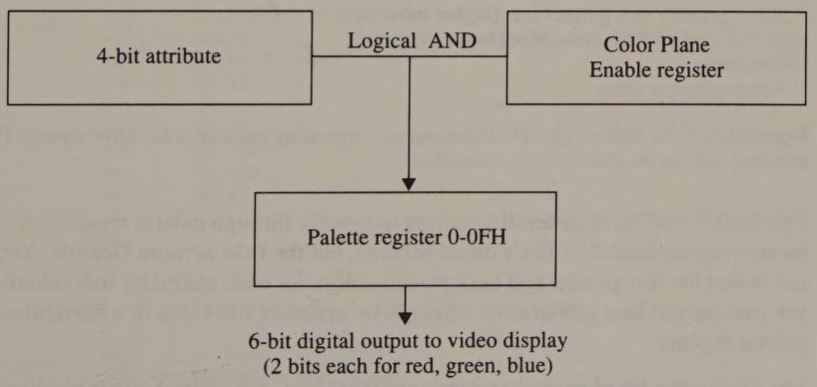

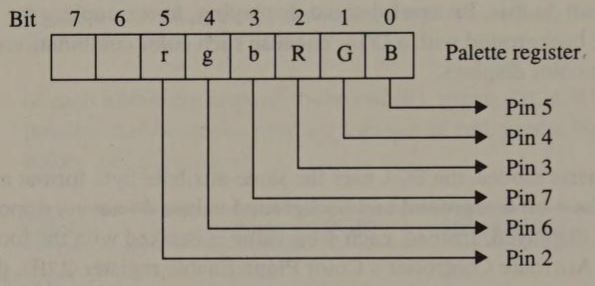

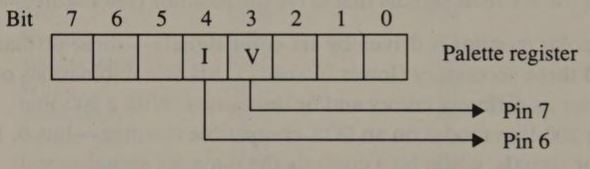

The Attribute Controller supports a 16-color palette on the EGA and VGA. It also controls the color displayed during overscan intervals. The Attribute Controller's Address register and 21 data registers all map to I/O port 3C0H (see Figure 2-17). A value written to port 3C0H will be stored in either the Address register or a data register, depending on the state of a flip-flop internal to the Attribute Controller.

| Register | Name |

|---|---|

| 0-0FH | Palette |

| 10H | Attribute Mode Control |

| 11H | Overscan Color |

| 12H | Color Plane Enable |

| 13H | Horizontal Pixel Panning |

| 14H | Color Select (VGA only) |

To set the flip-flop, perform an I/O read (IN AL,DX) of the CRT Status register (port 3BAH in monochrome modes, 3DAH in color modes). Listing 2-3 illustrates how this is done in updating an Attribute Controller register. On the VGA, Attribute Controller data registers may be read as well as written. Do this by writing the register number to port 3C0H and then reading the value from port 3C1H.

; program the Attribute Controller directly

mov ax,40h

mov es,ax ; ES := video BIOS data segment

mov dx,es[63h] ; DS := 3x4h (3B4h or 3D4h)

add dl,6 ; DX := 3xAh (CRT Status Register)

cli ; clear the interrupts

in al,dx ; reset Attribute Controller flip-flop

push dx ; preserve Status Reg port

mov dl, 0C0h ; DX := 3C0h

mov al, RegNumber

out dx, al ; write to Address Register

jmp $+2 ; waste a few cylces so that Attribute

; Controller can respond

mov al, DataValue

out dx, al ; write to data register

pop dx ; DX := 3xAh

in al, dx ; reset that flip-flop

mov dl, 0Ch

mov al, 20h ; restore palette

out dx, al

sti

; using the video BIOS

mov ax,1000h ; AH := 10h (INT 10h function number)

; AL := 0 (Set individual Attribute

; Controller register)

mov bl,RegNumber

mov bh,DataValue

int 10hYou can use 16-bit port writes (OUT DX,AX) to store data in EGA and VGA Sequencer and Graphics Controller registers. On the EGA, you can use the same technique to program the Attribute Controller, which recognizes I/O port writes at 3C1H as well as 3C0H. However, the VGA Attribute Controller does not emulate the EGA in this regard, so this technique should be used carefully when VGA compatibility is important.

The video BIOS supports a number of different video modes on IBM PC and PS/2 video subsystems (see Figure 2-18). The video BIOS routines, which can be called with INT 10H, let you establish a video mode simply by specifying its number.

Not all of the BIOS video modes are available on all IBM PC video subsystems. Furthermore, the video BIOS does not support video mode configurations on non-IBM hardware unless it exactly emulates the corresponding IBM hardware.

For example, all Hercules video adapters emulate IBM's MDA exactly. Thus, the video BIOS can be used to select the monochrome alphanumeric mode (BIOS mode 7) on all Hercules products. However, the Hercules hardware also supports a 720-by-348 graphics mode which is not recognized by IBM's video BIOS. Consequently, to set up the Hercules graphics mode, a program must configure the hardware directly (see Listing 2-4.)

| Mode Number (hex) | Resolution | Colors | Mode Type | Buffer Segment | MDA | CGA | EGA | MCGA | VGA

|

|---|---|---|---|---|---|---|---|---|---|

| 0 | 40x25 chars (320x200 pixels)*,† | 16 | Alpha | B800 | x | x | x | x | |

| 0 | 40x25 chars (320x350 pixels)† | 16 | Alpha | B800 | x | x | |||

| 0 | 40x25 chars (320x400 pixels) | 16 | Alpha | B800 | x | ||||

| 0 | 40x25 chars (360x400 pixels)† | 16 | Alpha | B800 | x | ||||

| 1 | 40x25 chars (320x200 pixels)† | 16 | Alpha | B800 | x | x | x | x | |

| 1 | 40x25 chars (320x350 pixels)† | 16 | Alpha | B800 | x | x | |||

| 1 | 40x25 chars (320x400 pixels) | 16 | Alpha | B800 | x | ||||

| 1 | 40x25 chars (360x400 pixels)† | 16 | Alpha | B800 | x | ||||

| 2 | 80x25 chars (640x200 pixels)*,† | 16 | Alpha | B800 | x | x | x | x | |

| 2 | 80x25 chars (640x350 pixels)† | 16 | Alpha | B800 | x | x | |||

| 2 | 80x25 chars (640x400 pixels) | 16 | Alpha | B800 | x | ||||

| 2 | 80x25 chars (720x400 pixels)† | 16 | Alpha | B800 | x | ||||

| 3 | 80x25 chars (640x200 pixels)† | 16 | Alpha | B800 | x | x | x | x | |

| 3 | 80x25 chars (640x350 pixels)† | 16 | Alpha | B800 | x | x | |||

| 3 | 80x25 chars (640x400 pixels) | 16 | Alpha | B800 | x | ||||

| 3 | 80x25 chars (720x400 pixels)† | 16 | Alpha | B800 | x | ||||

| 4 | 320x200 pixels | 4 | Graphics | B800 | x | x | x | x | |

| 5 | 320x200 pixels‡ | 4 | Graphics | B800 | x | x | x | x | |

| 6 | 640x200 pixels | 2 | Graphics | B800 | x | x | x | x | |

| 7 | 80x25 chars (720x350 pixels)† | 2 | Alpha | B000 | x | x | x | ||

| 7 | 80x25 chars (720x400 pixels)† | 2 | Alpha | B000 | x | ||||

| 8 | (PCjr only) | ||||||||

| 9 | (PCjr only) | ||||||||

| 0A | (PCjr only) | ||||||||

| 0B | (used by EGA video BIOS) | ||||||||

| 0C | (used by EGA video BIOS) | ||||||||

| 0D | 320x200 pixels | 16 | Graphics | A000 | x | x | |||

| 0E | 640x200 pixels | 16 | Graphics | A000 | x | x | |||

| 0F | 640x350 pixels | 2 | Graphics | A000 | x | x | |||

| 10 | 640x350 pixels§ | 4 | Graphics | A000 | x | ||||

| 10 | 640x350 pixels | 16 | Graphics | A000 | x | x | |||

| 11 | 640x480 pixels | 2 | Graphics | A000 | x | x | |||

| 12 | 640x480 pixels | 16 | Graphics | A000 | x | ||||

| 13 | 320x200 pixels | 256 | Graphics | A000 | x | x |

*On the CGA, the color burst component of the composite video signal is disabled. This improves the appearance of a monochromatic green or amber display. On the EGA, MCGA and VGA, mode 0 is the same as mode 1, and mode 2 is the same as mode 3.

†On the VGA, the vertical resolution of this mode is selected using INT 10H function 12H (see Appendix A).

‡On the CGA, color burst is disabled and the four-color palette contains black, cyan, red and white (for details, see chapter 4). On the EGA, MCGA and VGA, mode 5 is the same as mode 4.

§Only four colors can be displayed on an EGA with only 64KbB of video RAM.

Listing 2-4. Configuring a Hercules adapter for 720-by-348 graphics

mode

TITLE 'Listing 2-4'

NAME HercGraphMode

PAGE 55,132

;

; Name: HercGraphMode

;

; Function: Establish Hercules 720x348 graphics mode on HGC, HGC+, InColor

;

; Caller: Microsoft C:

;

; void HercGraphMode();

;

DGROUP GROUP _DATA

_TEXT SEGMENT byte public 'CODE'

ASSUME cs:_TEXT,ds:DGROUP

PUBLIC _HercGraphMode

_HercGraphMode PROC near

push bp ; preserve caller registers

mov bp,sp

push si

push di

; Update Video BIOS Data Area with reasonable values

mov ax,40h

mov es,ax

mov di,49h ; ES:DI := 0040:0049 (BIOS data area)

mov si,offset DGROUP:BIOSData

mov cx,BIOSDataLen

rep movsb ; update BIOS data area

; Set Configuration Switch

mov dx,3BFh ; DX := Configuration Switch port

mov al,1 ; AL bit 1 := 0 (exclude 2nd 32K of

; video buffer)

; AL bit 0 := 1 (allow graphics mode

out dx,al ; setting via 3B8h)

; Blank the screen to avoid interference during CRTC programming

mov dx,3B8h ; DX := CRTC Mode Control Register port

xor al,al ; AL bit 3 := 0 (disable video signal)

out dx,al ; blank the screen

; Program the CRTC